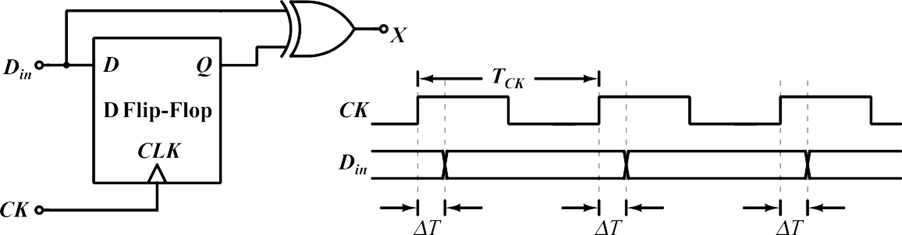

Q. In the circuit shown below, a positive edge-triggered D Flip-Flop is used for sampling input data 𝐷𝑖𝑛 using clock 𝐶𝐾. The XOR gate outputs 3.3 volts for logic HIGH and 0 volts for logic LOW levels. The data bit and clock periods are equal and the value of Δ𝑇/𝑇𝐶𝐾 = 0.15, where the parameters Δ𝑇 and 𝑇𝐶𝐾 are shown in the figure. Assume that the Flip-Flop and the XOR gate are ideal.

If the probability of input data bit (𝐷𝑖𝑛) transition in each clock period is 0.3, the average value (in volts, accurate to two decimal places) of the voltage at node 𝑋, is

Ans: 0.82 – 0.86

![Determine the correctness (or otherwise) of the following Assertion [A] and the Reason [R]](https://www.gkseries.com/blog/wp-content/uploads/2023/10/Determine-the-correctness-or-otherwise-of-the-following-Assertion-A-and-the-Reason-R.jpg)